ddApp-10

Sayısal Tasarım ve FPGA Uygulamaları

7 Segment Display Uygulaması

| Durum | Tamamlandı |

| Tarih | 8 Nisan 2023 |

| Hazırlayan | Dilay GÖRKEN |

| E-Posta | dilaygorken2512@gmail.com, info@beti.com.tr |

Amaç

Bu doküman Basys 3 kartı üzerindeki 7 Parçalı göstergenin özelliklerini ve nasıl kullanıldığını anlatmaktadır.

Giriş

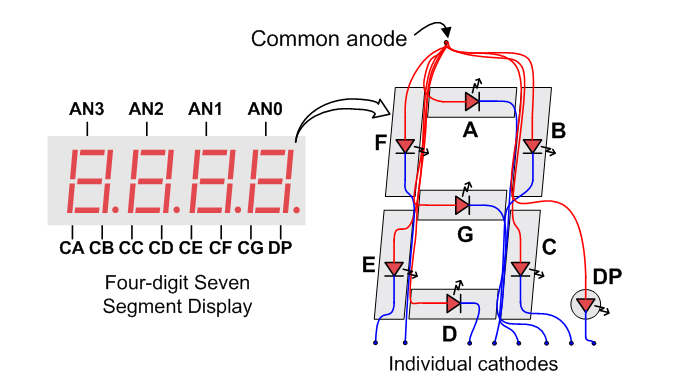

Kart üzerinde 4 adet 7-parçalı LED gösterge bulunmaktadır; her bir gösterge 7 parçadan oluşmuş ve “8” rakamı görüntüsündedir. Her parçadaki LED ayrı ayrı yanabilir, dolayısıyla bazı parçalar yanık, diğerleri sönük konumda 128 değişik kalıp görüntülenebilir. Bu 128 adet kalıptan 10’luk hanelere karşılık gelenler uygulamalar için en yararlı olanlarıdır.

4 adet 7-parçalı LED göstergenin anodları ortak bir anod (Common Anode) devresine bağlanmıştır. Fakat LED katodları ayrıdır. Ortak anot sinyali 4 hane “digit enable” sinyalini oluşturur. 4 hanedeki benzer parçaların katodları 7 adet devre noktasına bağlıdır. Bunlar CA’dan CG’ye kadar etiketlenmiştir.

Örneğin 4 hanenin 4 adet “D” birleşiktir ve “CD” etiketlidir. Bu 7 adet katod sinyali 4-hane görüntü biriminin giriş sinyalleridir. Bu bağlantı “zaman paylaşımlı” “time multiplexed” görüntüleme bağlantısıdır. Yani katod sinyalleri 4-hane için de ortaktır. Ancak hangi hanenin anod sinyali geçerli mantık seviyesine çekilmişse sadece o hane yanacaktır.

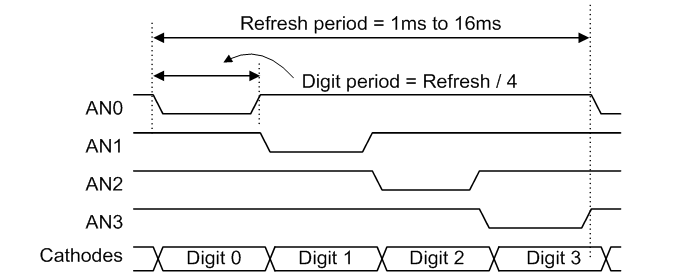

Taramalı bir görüntü denetleme devresi 4-haneli görüntü birimini kontrol edebilir. Bu devre herhane için anod sinyalini ve katod kalıplarını tekrarlı olarak gönderecektir. Tekrarlama frekansı insan göz algılama frekansından yüksek olmalıdır. Her hane tekrarlama periyodunun ¼’ü kadar süre yanık kalacaktır. Ancak insan gözü bir hanenin sönüp tekrar yandığını fark edemeyeceği için o haneyi sürekli yanık görecektir. Eğer tekrarlama veya “tazeleme” hızı 45 hertz civarına düşürülürse çoğu insan hanelerdeki görüntüyü titrek görecektir. Her dört hanenin parlak ve sürekli yanıyor görünmesi için her hane bilgisi 1 ile 16ms arasında tazelenmelidir ki bu da 1KHz ile 60Hz arasında değişen tazeleme frekansına karşılık gelecektir.

Örneğin 60Hz tazeleme frekansı uygulandığında tüm gösterge 16ms de bir değişecektir. Bu da her hanenin ¼ tazeleme periyodu, yani 4ms de bir veri yenilenmesi gerektiğini gösterecektir. Bu nedenle gösterge denetleme devresinin doğru katod bilgisini anod aktif edildiğinde hazır etmesi gerekecektir. Şekilde tazeleme işlemi örneklenmiştir. Görüldüğü gibi eğer AN1 aktif edildiğinde CB ve CC aktif edilirse 1. hanede “1” rakamı görüntülenecektir. Diğer bir örnekte AN2 aktif edildiğinde CA, CB ve CC aktif edilirse 2. hanede “7” rakamı görüntülenecektir. Eğer A1 ve CB, CC 4ms süreyle sürülür ve A2, CA, CB, CC de 4ms süreyle tekrarlı sürülür ise, görüntüleme biriminin ilk iki hanesinde “17” görüntülenecektir.

Deney Tanıtımı

Bu deneyde Basys 3 kullanılarak, seven-segment göstergelerde bir sayıcı tasarlanmıştır. Sayıcı her göstergeyi kendi içinde 0’dan 9’a tüm segmentleri de sayıcı mantığına uyacak şekilde çalıştırır.

- • Sayıcı; 1 saniye aralıklarla, 1 artarak, 9’a ulaşmalı.

- • Sonrasında ise 4’lü anotlardan hangisinde ilerlemesi gerektiğini anlayarak anot seçimi yapmalıdır.

- • 1 saniye aralık takibini 100MHz clock sinyali kullanan Basys 3 ile oluşturabilmek için saat bölme uygulanmalıdır.

- • Anot seçimi ve sayıcı frekansı belirlendikten sonra ekrana led’leri yakma işlemi bu düzene uygun seven-segment-decoder’ı ile tamamlanmalıdır.

Aşağıdaki bağlantıda bu deney için gerekli deney kodları bulunmaktadır:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity örnek is

port (

s : in std_logic;

r : out std_logic

);

end örnek;

architecture behavioral of örnek is

begin

r <= s;

end behavioral;

Deneyin Yapılışı

- Kişisel bilgisayarınıza Seven-Segment-Display Klasörünü indiriniz

- İndirdiğiniz "zip" dosyasını, belirteceğiniz bir klasöre ayıklayınız.

- Eğer kişisel bilgisayarınızda bulunmuyor ise; "Xilinx Vivado 2020.2" veya son sürümlerinden birini kurunuz.

- Ayıkladığınız dosyaların içindeki ".xpr" Vivado Project File dosyasına çift tıklayarak veya birlikte aç -> Vivado ile açınız.

- Projeniz açıldığında proje ekranının sağ üst köşesinde "write_bitstream_Complate" ve ✅ görüyorsanız projeniz board'a aktarım için hazırdır.

- Eğer "Synthesis and Implementation Out-of-date" yazısını görüyorsanız: Vivado flow navigator'dan "Program and Debug" altındaki "Generate Bitstream" e tıklayınız. Launch Runs ekranından "OK" a tıklayarak devam ediniz. Bu işlem biraz zaman alabilir. write_bitstream_Complate'i gördükten sonra yine "Program and Debug" altındaki 'Open Hardware Manager' butonuna tıklayınız. Bu aşamada USB ile Basys3'ü kişisel bilgisayarınıza bağlayınız.

- Basys3 üzerindeki 'power' ledinden cihazın güç alıp almadığını anlayabilirsiniz. 'power' ledi yanmıyorsa: power switch'ini açık konuma getirmemiş veya bağlantı kablonuzda bir sıkıntı yaşıyor olabilirsiniz.

- Power ledi yandığından yine Vivado üzerinden 'Open hardware Manager' altındaki "open Target" -> "auto connect" butonuna tıklayınız. Bu Kişisel bilgisayarınız ile FPGA arasındaki bağlantıyı otomatik olarak sağlayacaktır.

- Bağlantı başarısısz olursa vivado size bir uyarı verecektir. Bu durumda adımları tekrarlayıp tekrar deneyiniz.

- Bağlantı kurulduktan sonra cihazımızı programlayabiliriz. Cihazı programlamak için 'Open Hardware Manager' altındaki "program Device" butonuna tıklayalım.

- Program Device bloğu önümüze, programlama yapmak için hangi '.bit' dosyasını kullanacağını soracaktır. .bit dosyaları projemizin içinde var olduğundan vivadonun otomatik yerleştirdiği bit dosyasını kullanarak devam ediniz ve "Program" butonuna basınız.

- Basys3'ü programladık. Programı resetlemek isterseniz board üzerindeki "PROG" butonunu kullanabilirsiniz

Telif Hakkı

Bu doküman, Beti Elektronik San. ve Tic. Ltd. Şti’nin fikri mülkiyetine tabidir ve firmanın izni olmadan kopyalanması, çoğaltılması, dağıtılması veya yeniden yayınlanması yasaktır. Kitabın herhangi bir bölümünün veya içeriğinin izinsiz kullanılması, telif hakkı ihlali anlamına gelir ve yasal işlemlere yol açabilir. Dokümanın içeriği veya herhangi bir kısmı kullanılacaksa, yazılı izin alınmalıdır. İzin talepleri için info@beti.com.tr ile iletişime geçiniz. Makul alıntılar yapılabilir, ancak bu alıntılar mutlaka kaynak gösterme ile birlikte sunulmalıdır. Kaynak göstermeden yapılan alıntılar veya içerik kullanımları, yine telif hakkı ihlali olarak kabul edilir.